- SIMD

-

Классификация по Флинну Одиночный поток команд

(Single Instruction)Множество потоков команд

(Multiple Instruction)Одиночный поток данных

(Single Data)SISD

(ОКОД)MISD

(МКОД)Множество потоков данных

(Multiple Data)SIMD

(ОКМД)MIMD

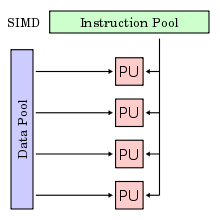

(МКМД)SIMD (англ. single instruction, multiple data — одиночный поток команд, множественный поток данных, ОКМД) — принцип компьютерных вычислений, позволяющий обеспечить параллелизм на уровне данных.

SIMD-компьютеры состоят из одного командного процессора (управляющего модуля), называемого контроллером, и нескольких модулей обработки данных, называемых процессорными элементами. Управляющий модуль принимает, анализирует и выполняет команды. Если в команде встречаются данные, контроллер рассылает на все процессорные элементы команду, и эта команда выполняется на нескольких или на всех процессорных элементах. Каждый процессорный элемент имеет свою собственную память для хранения данных. Одним из преимуществ данной архитектуры считается то, что в этом случае более эффективно реализована логика вычислений. До половины логических инструкций обычного процессора связано с управлением выполнением машинных команд, а остальная их часть относится к работе с внутренней памятью процессора и выполнению арифметических операций. В SIMD компьютере управление выполняется контроллером, а «арифметика» отдана процессорным элементам.

Векторные процессоры также использовали принцип SIMD, одной командой могли обрабатываться векторы размером до нескольких тысяч элементов.

SIMD-расширения различных архитектур

Короткие SIMD инструкции (64 или 128 бит) стали появляться в процессорах общего назначения в 1990-ых годах. В разной степени следующие процессорные архитектуры поддерживют SIMD-расширения или SIMD-инструкции:

- DEC Alpha - Motion Video Instructions (MVI)

- IBM PowerPC: AltiVec, SPE

- HP's PA-RISC Multimedia Acceleration eXtensions (MAX)

- Intel: MMX, iwMMXt, SSE, SSE2, SSE3 SSSE3, SSE4.x

- AMD: 3DNow!

- ARC: ARC Video subsystem

- SPARC: VIS, VIS2

- Sun MAJC,

- ARM: NEON

- MIPS: MDMX (MaDMaX), MIPS-3D

Группа из IBM, Sony, Toshiba совместно разработала для процессора Cell Processor сопроцессор SPU, набор команд которого в значительной степени использовал SIMD. NXP (Philips) разработала несколько SIMD процессоров Xetal, в котором имелось 320 процессорных элементов, работавших с 16 битными данными.

Современные видеоускорители (GPU) обычно основаны на SIMD-архитектуре с поддержкой векторов длины 128, 256 или более бит.

Расширение AVX компании Intel предоставляет набор SIMD-инструкций для обработки данных в формате с плавающей запятой в группах длиной 256 бит. Сопроцессоры Intel MIC включают в себя 512-битный набор инструкций.

x86-совместимые процессоры

Информация в этой статье или некоторых её разделах устарела. Вы можете помочь проекту, обновив её и убрав после этого данный шаблон.- MMX — Multimedia Extensions. Коммерческое название дополнительного набора инструкций, выполняющих характерные для процессов кодирования/декодирования потоковых аудио/видео данных действия за одну машинную инструкцию. Впервые появился в процессорах Pentium MMX.

- MMX Extended — расширенный набор инструкций MMX, используемый в процессорах AMD и Cyrix.

- 3DNow! — расширение набора команд MMX процессоров AMD, начиная с AMD K6-2.

- 3DNow! Extended — расширение набора команд 3DNow! процессоров AMD, начиная с AMD Athlon.

- SSE — набор инструкций, разработанный Intel, и впервые представленный в процессорах серии Pentium III

- SSE2 — набор инструкций, разработанный Intel, и впервые представленный в процессорах серии Pentium 4.

- SSE3 — третья версия SIMD-расширения Intel, потомок SSE, SSE2 и x87. Представлен 2 февраля 2004 года в ядре Prescott процессора Pentium 4.

- SSSE3 — набор SIMD-инструкций, используемый в процессорах Intel Core 2 Duo.

- SSE4 — новая версия SIMD-расширения Intel. Анонсирован 27 сентября 2006 года. Представлен в 2007 году процессорах серии Penryn.

- AVX — анонсированная версия SIMD-расширения Intel, которая представлена в 2010 году в процессорах архитектуры Sandy Bridge.

В этой статье не хватает ссылок на источники информации. Информация должна быть проверяема, иначе она может быть поставлена под сомнение и удалена.

Вы можете отредактировать эту статью, добавив ссылки на авторитетные источники.

Эта отметка установлена 20 декабря 2012.Наборы расширения базовых инструкций процессоров семейства x86 MMX | MMXEXT | SSE | SSE2 | SSE3 | SSSE3 | SSE4 | ATA | 3DNow! | 3DNowExt | SSE5 | AVX | AES Технологии цифровых процессоров Архитектура CISC · EDGE · EPIC · MISC · URISC · RISC · VLIW · ZISC · Фон Неймана · Гарвардская

8 бит · 16 бит · 32 бит · 64 бит · 128 битПараллелизм Pipeline Конвейер · In-Order & Out-of-Order execution · Переименование регистров · Speculative execution Уровни Бит · Инструкций · Суперскалярность · Данных · Задач Потоки Многопоточность · Simultaneous multithreading · Hyperthreading · Superthreading · Аппаратная виртуализация Классификация Флинна SISD · SIMD · MISD · MIMD Реализации DSP · GPU · SoC · PPU · Векторный процессор · Математический сопроцессор • Микропроцессор · Микроконтроллер Компоненты Barrel shifter · FPU · BSB · MMU · TLB · Регистровый файл · control unit · АЛУ • Демультиплексор · Мультиплексор · Микрокод · Тактовая частота • Корпус • Регистры • Кэш (Кэш процессора) Управление питанием APM · ACPI · Clock gating · Динамическое изменение частоты • Динамическое изменение напряжения  Категории:

Категории:- Технологии процессоров

- Архитектура компьютеров

- Параллельные вычислительные системы

Wikimedia Foundation. 2010.